vivado_18.3_AR71948_patch

”vivado 18.3 patch AR71948“ 的搜索结果

所有IP核都可用

Modelsim+Vivado安装和联合仿真教程

要激活Vivado 18.3,您可以按照以下步骤进行操作: 1. 首先,您需要下载Vivado 18.3的安装文件。您可以在参考提供的链接中找到安装文件,并使用提取码2k9z进行解压。 2. 解压后,打开Vivado 18.3的安装文件夹,...

- *1* *2* *3* [Vivado18.3的安装 安装教程](https://blog.csdn.net/weixin_42151221/article/details/103225226)[target="_blank" data-report-click={"spm":"1018.2226.3001.9630","extra":{"utm_source":"vip_...

很高兴为您提供Vivado 18.3的安装教程。请按照以下步骤进行操作: 1. 首先,您需要从Xilinx官方网站下载Vivado Design Suite 18.3的安装程序。您可以在Xilinx的网站上注册并登录,然后选择合适的版本进行下载。 2....

Vivado 18.3 是一款由 Xilinx 公司开发的集成电路设计工具。它提供了一个全面的开发环境,用于设计、验证和实现 FPGA(可编程逻辑门阵列)和 SoC(系统级芯片)应用。Vivado 18.3 版本具有许多改进和新功能,包括更...

- *1* *2* *3* [Vivado18.3的安装 安装教程](https://blog.csdn.net/weixin_42151221/article/details/103225226)[target="_blank" data-report-click={"spm":"1018.2226.3001.9630","extra":{"utm_source":"vip_...

你可以在Xilinx官方网站上找到Vivado 18.3的下载页面。在该页面上,你需要登录你的Xilinx账户,并按照指示下载Vivado 18.3软件。如果你还没有Xilinx账户,可以创建一个新的账户然后登录进行下载。记得在下载前确认你...

好的,关于vivado18.3的安装,您可以按照以下步骤进行: 1. 首先,您需要从Xilinx官网下载Vivado Design Suite 2018.3的安装文件。 2. 下载完成后,解压缩文件并运行安装程序。 3. 在安装程序中,您需要选择要安装...

要打开 Vivado 18.3 中导出的 ILA 数据,请按照以下步骤进行: 1. 在 Vivado 中打开你的项目。 2. 在左侧导航栏中,选择 "Open Hardware Manager"。 3. 在 "Hardware Manager" 窗口中,选择 "Open Target"。 4. ...

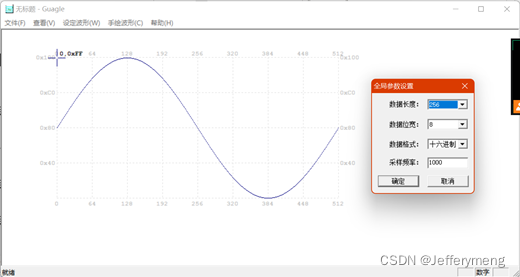

vivado基础使用方法

对vivado2018.2的基本使用流程做了一个详细说明.以一个流水灯入门工程为例子,说明了工程的建立,综合,实现,下板调试. 里面涵盖了vivado关联第三方代码编辑器,vivado关联第三方仿真软件,vivado软件的基本开发流程。...

安装完成Vivado18.3 SE之后桌面会有4个快捷方式(DE没有System Generator) Vivado 2018.3:这就是最常用的。也是对PS和PL端开发的主要工具。 Vivado HLS 2018.3:这是HLS(High Level Synthesis)工具,可以实现...

ZYNQ的开发不论是PL还是PS端都是要从Vivado中的创建工程开始,所以和PL端开发一样,首先打开Vivado18.3。 2. 创建工程 2.1 Porject Name 同PL端开发一样,PS端同样需要创建工程。 创建好工程路径和工程名称后...

vivado2018.3关于microblaze程序不能嵌入到bit文件里的补丁,补丁下载解压后,直接复制到vivao相应的安装目录下

最详细手把手教你安装 Vivado2018.3

发现出现这一问题的原因是vivado18.3上一次打开的工程影响的,找到最近一次打开的vivado工程路径,将工程全部删掉,重新打开vivado18.3,可以正常使用,正常在线加载程序调试了。

重新综合时,发现进度条一直为0,对代码进行还原后还是不行,查看log窗口的进度信息,是空白的,把分析综合取消,重新综合问题还是没解决,发现电脑上已关闭360杀毒软件,把电脑重启后,重新打开vivado18.3,...

推荐文章

- 1.2亿次下载,近3万Star的开源项目是为何会“死”掉?-程序员宅基地

- sol2 二 教程:快速入门-程序员宅基地

- 基于学生网上选课系统的设计与实现-程序员宅基地

- OpenAI Sora模型,官方技术文档翻译_openai-sora+技术文档-程序员宅基地

- 在PyTorch中搭建神经网络的基础知识-程序员宅基地

- (免费领源码)java#springboot#mysql开放实验室管理系统03361-计算机毕业设计项目选题推荐-程序员宅基地

- 现代控制理论(4)——李雅普诺夫稳定性理论_李亚普诺夫稳定性-程序员宅基地

- 大电流dcdc降压芯片20a_基于MC34063芯片DC-DC(20-5)降压型变换电路-程序员宅基地

- About Add DataRow-程序员宅基地

- linux中-f的含义,linux 下shell中if的“-e,-d,-f”的含义-程序员宅基地